# Novel Concept of Reducing OVR at the Output of SEPIC Converter using Programmable Capacitors

Danish Iqbal<sup>1</sup>, Muhammad Siddique<sup>1</sup>, Akmal Chaudhary<sup>2</sup>, M Kamran Liaqat bhatti<sup>1</sup>, Abdul Sattar Malik<sup>3</sup>, Muhammad Abrar<sup>3</sup>, and Mujahid Hussain<sup>1</sup>

<sup>1</sup>Electrical Engineering Department, NFC IET Multan, Pakistan. <sup>2</sup>College of E&IT Ajman University, UAE. <sup>3</sup>Electrical Engineering Department, UCET BZU Multan, Pakistan. danishiqbal6050@gmail.com, engr.siddique01@gmail.com, m.akmal@ajman.ac.ae, dr\_mklbhatti@nfciet.edu.pk, maliksattar777@bzu.edu.pk, mabrar@bzu.edu.pk, mujahid.m41@gmail.com, kumail.f05@gmail.com

*Abstract:* In this paper, a novel methodology is proposed to reduce output voltage ripple (OVR) of the single-ended primary-inductor-converter (SEPIC). The mathematical analysis of the SEPIC converter is performed to compute suitable values of capacitance and switching frequency for optimal reduction in the OVR. The OVR in SEPIC converter is analyzed in the presence of two- dimensional effect: first by varying the values of the programmable capacitor using digital controller; second by changing the switching frequency of the switching signal. The comprehensive mathematical analysis of the OVR in SEPIC is performed for three modes. The obtained results of proposed methodology for the reduction of the OVR in SEPIC converter are verified through MATLAB simulation.

| Table 1. List of Symbols     |                 |

|------------------------------|-----------------|

| Description                  | Symbols         |

| Input Voltage                | Yi              |

| Output Voltage               | Yo              |

| Variable Capacitor           | $\Delta C_2$    |

| Output Voltage Ripple (OVR)  | μ               |

| Change in OVR                | V               |

| Change in OVR                | ñ               |

| switching frequency          | F               |

| Time                         | Т               |

| Duty cycle                   | D               |

| Critical Inductor            | X               |

| Equivalent Critical Inductor | E               |

| Load Current                 | $i_{Load}$      |

| Equivalent Inductance        | L <sub>eq</sub> |

Keywords: SEPIC Converter; Output voltage ripple; Digital capacitor; Switching frequency.

# 1. Introduction

Today, converters are extensively used in electrical devices and systems such as aeronautical applications [1], DC power supply [2], [3], fuel cell [4], automobiles [5], electrical vehicles [6], [7], control of power factor [8] and DC power lightening system [9]. There are different types of converters which include buck converter, boost converter, buck-boost converter, Cuk converter, Zeta converter and etc. The continuous research efforts have resulted in the expanse of the power electronics'. Many researchers have made extensive efforts to examine the output behavior of converters by small modifications in their circuits. Since the main components of the PWM converter circuit include inductors and capacitors and it is a well-established fact that there is no

Received: January 21<sup>st</sup>, 2020. Accepted: June 24<sup>th</sup>, 2021 DOI: 10.15676/ijeei.2021.13.2.14 power loss when power exchange between a pure inductor and a pure capacitor takes place. The PWM switching signals can be used to control the transfer of power from input to output when the resonant switching frequency is lower than the switching frequency of the inductor-capacitor network [10]. The most popular PWM converter is buck converter and all other converters are developed based on the same approach that is used for buck converters [11]. These include boost converter [11], [12], buck-boost converter [11], [13], SEPIC converter [12], [14], Zeta converter [14], [15], flyback [16] and Cuk converter [17]. Many other PWM converters are produced by putting the dc transformers in buck-boost converter, for example, full-bridge, half-bridge, pushpull and etc [18]. The advancement in PWM converters has been crossing over a century for now; in addition, many other converters have been manufactured, for example, quasi-resonant [19], Zsource [20] and switched-inductor hybrid converters [21], and these converters are performing optimally in several appliances successfully. Many researchers proposed an idea to produce PWM converters by using switching cell method. Switching in capacitor and inductor makes it possible to produce dc/dc converter, which is helpful to obtain a huge step-up or stepdown conversion [22]. The output of the DC/DC power converter is the regulated voltage because the output of the power converters is controlled and regulated by switching techniques [23]. This, subsequently, results in ripple in the output voltage of these power converters. This unwanted output voltage ripple (OVR) decreases the working efficiency of power converters [24]. Many researchers have rendered some methodologies to minimize the OVR in the converter's output. A complicated control approach in [25] is developed using a PID controller with a resonant controller paralleled to minimize the OVR. A new remodeled buck-boost converter by allegory has been introduced which has continuous output current and low current stress for components but it has a limited range of voltage conversion [26]. Buck-boost converter with an extra LC filter has been introduced to reduce the OVR but it is expensive and complicated [27]. Being complex this method can only be used for low voltages and high current. In addition, high electromagnetic interference is produced by using more elements such as capacitors and inductors [28]. The authors have proposed a new idea of SEPIC converter for OVR minimization in continuous conduction mode (CCM) and discontinuous conduction mode (DCM).

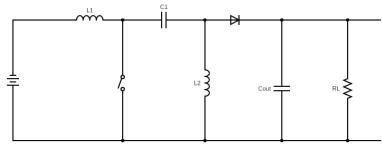

Figure 1. Circuit Diagram of SEPIC Converter

Figure 1 presents the circuit diagram of the SEPIC converter, which comprises of FET working as a switch and two inductors of suitable values along with the output capacitor [29][30]. The input side of the SEPIC converter is energized form a renewable DC energy source with an input voltage  $y_{in}$  and output voltage  $y_{out}$  is available at the output side. The working of a SEPIC converter is similar to any other conventional buck-boost converter with the difference that polarity of the output voltage is the same as the input voltage whereas in buck-boost converter the output polarity is opposite to the input polarity [31]. The ripple current and voltages are considerably high at the output [32]. In [33] tried to reduce OVR in converters by using critical inductor in both continuous conduction mode and discontinuous conduction mode.

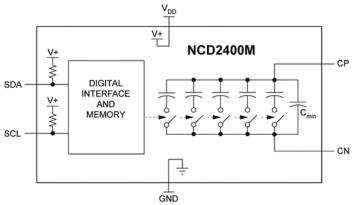

In this article, a new methodology is introduced which uses a programmable capacitor [34] and alteration in switching frequency. The schematic of programmable capacitor circuit is presented in Figure 2.

Figure 2. Schematics of programmable capacitor [32]

This article has three main sections: Section 2, describes the flow of energy in CCM mode and DCM mode and also gives the information about load current and inductors' current. Section 3, describes evaluation of the equivalent critical inductance in operational modes because this acts as a main boundary between CCM and DCM. Also, OVR minimization methodology is elaborated in detail. In section 4, the results of CISM-CCM, IISM-CCM and IISM-DCM in both buck and boost mode of a SEPIC converter are presented.

#### 2. Energy Transfer in Modes of Sepic

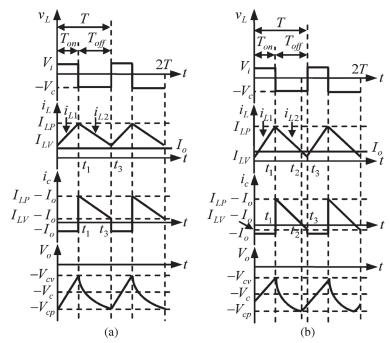

The working operation of the SEPIC converter consists of two modes, continuous conduction mode (CCM) and discontinuous conduction mode (DCM) as shown in Figure 3. The Boundary between these two modes is a specific value of inductor. This called as the equivalent critical inductor ( $\xi$ ) [35]. The (CCM) and (DCM) are further divided into complete induction supply mode (CISM), Incomplete induction supply mode (IISM) respectively. In Continuous Conduction Mode (CCM) the value of current in both inductors is positive and remains the same during the whole time. In CISM load current  $i_{Load}$  is less than the sum of currents in both inductors  $L_1$  and  $L_2$ , whereas in IISM mode the total current of both inductors is lower than the load current *i*Load. Complete Induction Supply Mode: The sum of both inductors currents is higher than the load current Load. During the time interval ton the voltages of both inductors are considered as yin and  $y_{C1}$  remains constant, while the current of both inductors  $i_{L1}$  and  $i_{L2}$  rises gradually from least possible value to maximal value. At the same time, capacitor current  $i_{Cl}$  is the same as inductor current  $i_{L2}$  but has negative value. Capacitor current  $i_{C1}$  decreases gradually, while the voltages of capacitor  $C_2$  becomes y<sub>out</sub>, with the diode being reverse biased. The current  $i_{Load}$  is given by capacitor  $C_2$ . Suppose that for a large value of capacitor  $C_2$  the load current  $i_{Load}$  is stable and  $y_{out}$ is diminished from high value to low value. At time interval toff, the output voltage is negative chronologically, while the current of both inductors is fallen from  $(i_{LP1} \& i_{LP2}) to (i_{LV1} \& i_{LV2})$ gradually. When inductor  $L_1$  is discharged the capacitor is charged, therefore, it can be said that current of capacitor  $C_1$  is equal to the inductor  $L_1$  current. On the other hand, capacitor current  $C_2$ is equal to the sum of currents of both inductors  $(i_{L1}+i_{L2})$ . If any change occurs in inductors currents ( $i_{L1}\&i_{L2}$ ), the capacitor current also changes while at the same time,  $i_{Load}$  is less than the sum of  $i_{L1}$  and  $i_{L2}$ . The Voltage across the output is changed from lower value to higher value. The sequence of power flow in *incomplete inductor supply mode* as well as in the discontinuous conduction mode is similar to complete induction supply mode. Moreover, this sequence of operation in SEPIC converter is discussed in detail in [36].

Figure 3. Inductor voltage, inductor current, capacitor current, and output voltage waveforms of buck boost converter (a)CISM-CCM. (b)IISM-CCM.[33]

## 3. Calculation of Equivalent Critical Inductor in Operational Modes

From above discussion it can be inferred that there are two operational modes in SEPIC converter i.e. CCM and DCM, and these two modes can be differentiated by the equivalent critical inductor ( $\zeta$ ). Also, in CCM mode there are further two modes i.e. CISM and IISM. These two modes are separated by a critical value of the inductor ( $\chi$ ). The equivalent inductance  $L_{eq}$  is equal to parallel combination of  $L_1$  and  $L_2$ , but in IISM-CCM, the value of equivalent inductance  $L_{eq}$  can be varied between the equivalent lower value of critical inductor i.e. ( $\zeta$ ) and upper value of the critical inductor i.e. ( $\chi$ ). In DCM there is only IISM. In IISM-DCM the equivalent inductance  $L_{eq}$  is less than the critical inductance ( $\chi$ ). For the sake of mathematical analysis we start with the following equations which are mentioned in [37].

$$\frac{R_L (1-d)^2}{2f} = \xi$$

(1)

$$\frac{R_L(1-d)^2}{2fd} = \chi \tag{2}$$

$$t_{on} + t_{off}$$

(3)

The value of duty cycled ranges between 0 and 1. The upper value of critical inductance ( $\chi$ ) can be given by Eq. (2) and the lower value of critical inductance ( $\zeta$ ) can be obtained by Eq. (1). These equations are used for the case when SEPIC converter work in Continuous Conduction Mode (CCM). The duty cycle can be given by

$$\frac{yo}{(yo+yi)} = d \tag{4}$$

Novel Concept of Reducing OVR at the Output of SEPIC

So the value of the equivalent critical inductance ( $\zeta$ ) and the critical inductance ( $\chi$ ) can be expressed in the following equations by using the value of *d* in Eqs. (1), (2).

$$\frac{R_L(yi)^2}{2f(yi+yo)^2} = \xi$$

$$R_L(yi)^2 = \chi$$

(5)

$$\frac{1}{2f(yo)(yi+yo)^2} = \chi$$

(6)

Calculation of output voltage ripple in CISM-CCM

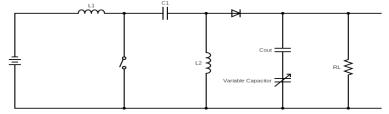

Figure 4. Proposed Methodology for SEPIC converter

The voltage ripple across the capacitor i.e. $\mu$  can be written as

$$\frac{-1}{C_2} \int_0^{t_{on}} iC_2(x) dx = \mu$$

<sup>(7)</sup>

At time interval  $(t_{on})$ , the value of  $(i_C 2)$  is following.

$$i_{C_2}(t_{on}) = -i_{Load} \tag{8}$$

Eq. (9) can be achieved by the utilitarian of Eqs.(3) and(8) in Eq.(7).

$$\frac{ti_{Load}d}{C_2} = \mu \tag{9}$$

Eq.(9) can further bare formed intoEq.(10), by using the values of time period t and load current, so get the following formula while  $t = \frac{1}{f}$  and  $i_{Load} = \frac{yo}{R_t}$ .

$$\frac{yo^2}{R_L f(C_2)(yi+yo)} = \mu$$

(10)

$\mu$  represents the output voltage ripple. Now we proceed further towards the crucial part of the proposed research which is the effect of variation of capacitor on the output voltage ripple. For analysing the effect of change in capacitor value on OVR, rewrite the Eq (7) by replacing the  $C_2$  with  $(C_2 + \Delta C_2)$ .

$$\frac{-1}{\Delta C_2 + C_2} \int_0^{t_{on}} iC_2(x) dx = \nu$$

(11)

By simplifying Eq. (11).

$$\frac{ti_{Load}d}{C_2 + \Delta C_2} = \nu \tag{12}$$

Put the value of  $i_{Load}$ , time period and duty cycle in above Eq. (12) to get the following equation.

$$\frac{yo^2}{R_L f(C_2 + \Delta C_2)(yi + yo)} = \nu$$

(13)

Eq. (13) illustrates the output ripple voltages by using a variable capacitor. The change in OVR can be written as

$$\mathcal{V} - \boldsymbol{\mu} = \tilde{\mathbf{n}} \tag{14}$$

Put the value of  $\mu$  and  $\nu$  from (10) and (13) respectively in Eq. (14).

$$\frac{yo^{2}}{R_{L}f(C_{2} + \Delta C_{2})(yi + yo)} - \frac{yo^{2}}{R_{L}fC_{2}(yi + yo)} = \mathbf{\tilde{n}}$$

$$-\frac{\Delta C_{2}yo^{2}}{C_{2}^{2} + C_{2}\Delta C_{2}R_{L}f(yi + yo)} = \mathbf{\tilde{n}}$$

(16)

$$C_2 + C_2 \Delta C_2 \kappa_L f(yl + yb)$$

(16)

The above equation elaborates the fact that the value of change in OVR i.e.  $\rho$  is dependent or

the value of capacitor and switching frequency. So, by using the digital capacitor or

programmable capacitor, we can control the output voltage ripple. Similarly, a suitable value of switching switching frequency canhelp in decreasing the OVR.

### B. Calculation of Output Voltage ripple in IISM-CCM

By taking integration of capacitor current  $i_{\text{C2}}$  and can get value of OVR at time duration from  $t_1$  to  $t_2$

$$\frac{1}{C_2} \int_{t_1}^{t_2} iC_2(x) dx = \mu \tag{17}$$

Eq. (18) elaborates the value of the capacitor current  $i_{C2}$ . When time is off [34].

$$i_{L1} + i_{L2} - i_{Load} = i_{C2} \tag{18}$$

Eq. (19) shows the value of the 1st inductor current.

$$i_{LP1} + \frac{yi - yo - y_{C1}}{L_1} = i_{L1}$$

(19)

Eq. (20) explains the value of the second inductor current.

$$i_{LP2} - \frac{y_0}{L_2} = i_{L2} \tag{20}$$

Eqs. (19) and (20) is achieved when  $t_1 = 0$  and the voltage of  $C_1$  is following.

$$y_{C1} = yi \tag{21}$$

Eq. (22) shows the value of  $t_2$

$$(i_{LP1} + i_{LP2} - i_{Load}) - \frac{Leq}{yo} = t_2$$

(22)

Resolving Eqs. (18), (22) when  $t_1 = 0$  and figure out new Eq. (23).

$$(i_{LP1} + i_{LP2} - i_{Load})^2 \frac{Leq}{2yoC_2} = \mu$$

(23)

Current of both inductors are:

$$i_{Load}\left[\frac{1}{1-d} + \frac{R_L}{2Leqf}(1-d)\right] = i_{LP1} + i_{LP2}$$

(24)

Apply Eqs. (4) and (24) in Eq. (23) then find a new Eq. (25).

$$\left(\frac{yi}{2Leqf(yi+yo)} + \frac{yo}{R_Lyi}\right)^2 \frac{Leqyo}{2C_2} = \mu$$

(25)

If use a variable capacitor in IISM - CCM. New Eq. (26) is achieved.

$$\frac{-1}{\Delta C_2 + C_2} \int_{t_1}^{t_2} iC_2(x) dx = v$$

(26)

Eq. (27) tells the value of the second current.

$$i_{L1} + i_{L2} - i_{Load} = i_{C2} \tag{27}$$

Put all the above Eqs. and do same process which performed in above section, then get the followingequation.

$$\left(\frac{yi}{2Leqf(yi+yo)} + \frac{yo}{R_Lyi}\right)^2 \frac{Leqyo}{2(C_2 + \Delta C_2)} = v$$

(28)

Put Eqs. (25) and (28) in Eq. (29)

$$\nu - \mu = \tilde{\mathsf{n}} \tag{29}$$

$$\left(\frac{yi}{2Leqf(yi+yo)} + \frac{yo}{R_Lyi}\right)^2 \frac{Leqyo}{2(C_2 + \Delta C_2)} = \varrho$$

(30)

$$\left(\frac{yi}{2Leqf(yi+yo)} + \frac{yo}{R_Lyi}\right)^2 \frac{Leqyo}{2C_2} - \frac{\Delta C_2 Leqyo}{2((C_2)^2 + C_2\Delta C_2)} \left(\frac{yi}{2Leqf(yi+yo)} + \frac{yo}{R_Lyi}\right)^2 = \tilde{n}$$

(31)

Eq. (31) define that change in OVR in IISM-CCM is depended upon capacitor value, switching frequency and input-output voltages.

C. Calculation of Output Voltage ripple in IISM-DCM

During the time duration from  $t_1$  to  $t_2$  as shown in Fig. 3 , the value of OVR can be achieved.

$$\frac{1}{C_2} \int_{t_1}^{t_2} iC_2(x) dx = \mu$$

(32)

$$(i_{LP1} + i_{LP2} - i_{Load})^2 \frac{Leq}{2C_2 yo} = \mu$$

(33)

Eq. (34) describes the value of the first inductor.

$$i_b + \frac{y_l}{L_1} dt = i_{LP1} \tag{34}$$

Eq. (35) is expressing the value of the second inductor.

$$\frac{y_l}{L_1}dt - i_b = i_{LP2} \tag{35}$$

Applying Eq.s (34), (35) in Eq. (33) and  $t = \frac{1}{f}$

$$\frac{Leq}{2C_2yo}\left(\frac{dyi}{Leqf} - i_{Load}\right)^2 = \mu \tag{36}$$

Eq. (37) presents the duty cycle value when converter works in DCM.

$$\frac{y_O}{y_i}\sqrt{\frac{2Leqf}{R_L}} = d \tag{37}$$

Apply Eq. (37) in Eq. (36) and put  $iLoad = \frac{yo}{R_L}$ . So get a new value of OVR.

$$\frac{Leqyo}{2C_2} \left(\sqrt{\frac{2}{fLeqR_L} - \frac{1}{R_L}}\right)^2 = \mu$$

(38)

If we use a variable capacitor in IISM-DCM.

$$\frac{-1}{\Delta C_2 + C_2} \int_{t_1}^{t_2} iC_2(x) dx = v$$

(39)

$$\frac{Leqvo}{2(C_2 + \Delta C_2)} \left(\sqrt{\frac{2}{fLeqR_L} - \frac{1}{R_L}}\right)^2 = \nu$$

(40)

If subtract Eq. (38) from Eq. (40) then achieve a new equation.

$$\begin{aligned}

\nu - \mu &= \mathbf{n}_{(41)} \\

\frac{Leqyo}{2(C_2 + \Delta C_2)} \left( \sqrt{\frac{2}{fR_L Leq}} - \frac{1}{R_L} \right)^2 \\

- \frac{Leqyo}{2C_2} \left( \sqrt{\frac{2}{fR_L Leq}} - \frac{1}{R_L} \right)^2 &= \mathbf{\tilde{n}}

\end{aligned}$$

(42)

By the simplification of Eq. (42) and gain Eq. (43), which is describing the value of the change in voltageripple by changing the value of capacitor.

$$-\frac{Leqyo\Delta C_2}{2(C_2^2 + C_2\Delta C_2)}\left(\sqrt{\left(\frac{2}{fR_L Leq}\right)} - \frac{1}{R_L}\right)^2 = \tilde{\mathsf{n}}$$

(43)

#### 4. Results and Discussion

To verify the proposed methodology decreasing the output voltage ripple in the SEPIC converter, MATLAB simulation environment is used. The results of different modes of proposed methodologies of reducing OVR are presented in the following paragraphs. There are two major modes of SEPIC Converter: continuous conduction mode (CCM) and discontinuous conduction mode (DCM), the CCM is divided into two categories; Complete Induction Supply Mode (CISM) and Incomplete Induction Supply Mode (IISM) whereas DCM has only Incomplete Induction Supply Mode (IISM). Each mode has three simulation results. The circuit element value soft proposed converter in buck mode are input voltage  $y_i$  is80V, output voltage  $y_o$  is 60 V, capacitor  $C_2$  is 28.5 mF, resistor is 50 ohm, switching frequency is 15 kHz with the change of 500Hz, variable capacitor  $\Delta C_2$  is 0.03mF. In boost mode values are: input voltage $y_i$  is 120 V, output voltage  $y_o$  is 150 V, capacitor  $C_2$  is 43 mF, resistor is 250 ohm, switching frequency is

15kHz with the change of 500Hz, variable capacitor  $\Delta C_2$  is 0.03mF and value of equivalent inductance  $L_{eq}$  is 0.4mH.

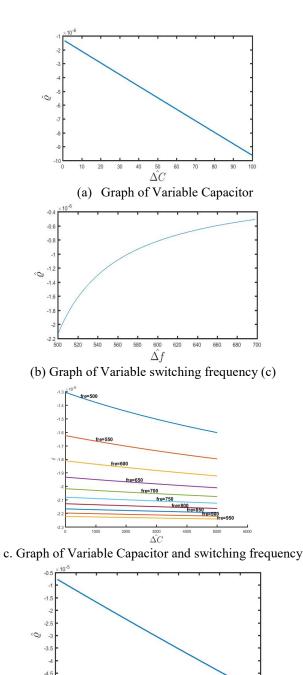

A. CISM-CCM

-5.5

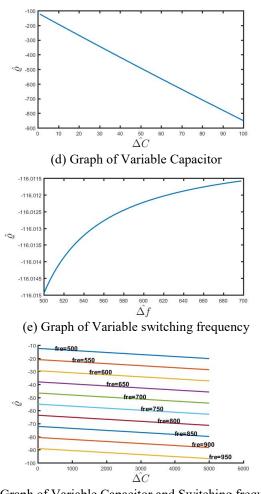

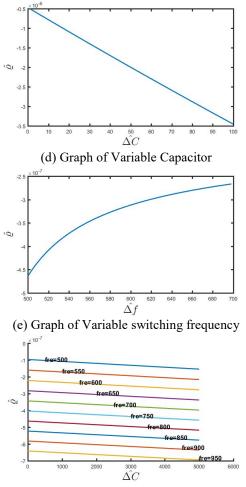

(f) Graph of Variable Capacitor and switching frequency Figure 5. change in output voltage ripple (Q) of buck and boost modes in IISM-CCM of SEPIC converter. (a) reports the result of a variable capacitor, (b) defines the result of a variable switching frequency and(c) represents the result of variable capacitor and switching frequency in buck mode while (d) states the result of a variable capacitor, (e) narrates the result of variable switching frequency and (f) defines the result of a variable capacitor and switching frequency in boost mode.

Figure 5 (a) describes the result in buck condition of the SEPIC converter. This result explains that with the minor change in  $\Delta C_2$  the value of change in output voltage ripples (o) changes. It means how much $\Delta C_2$  is increased, so the (o) decreases smoothly. Figure 5 (b) explains that the change in OVR ( $\rho$ ) with respect to switching frequency. Figure 5 (b) describes that the ( $\rho$ ) rises, when the switching frequency increases from 500 to 600 then it moves with slight change. In Figure 5 (c), not only the value of variable capacitor is changed but also the values of switching frequency are varied to produce present the simultaneous effect of both capacitance and switching frequency change. In Figure 5 (d), the resultant OVR of SEPIC in boost condition are presented with variation of capacitor value that the change  $\Delta C_2$  in output voltage ripples (g) also changes. It means how much  $\Delta C_2$  is increased so; the (o) also decreases smoothly. Figure 5(e) explains that the change in OVR  $(\rho)$  related to the switching frequency in boost mode. This process has the same values but slightly changes the value of switching frequency instead of variable capacitor. This figure describes that the (o) rises when the switching frequency is increased from 500 to 680 then it moves with slight change (almost constant). In Figure 5 (f) not only changes in the value of variable capacitor but also change in switching frequency are shown. In this process, remaining values are the same but with the slight variations in the variable capacitor and switching frequency values. In this Figure, it is noted that the change in OVR (Q) also varies with respect to switching frequency and variable capacitor  $\Delta C_2$ , at the start it produces a tremendous change in OVR (o) from -2 to -1.5 but gradually after this change grows in or and there is no the change in  $ovr(\rho)$  after -1.5.

#### B. IISM-CCM

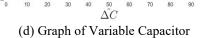

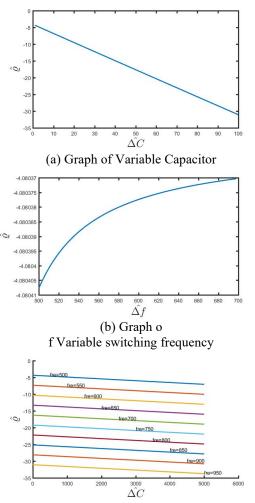

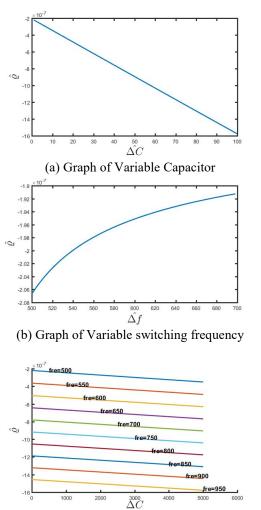

In buck condition of the SEPIC converter, Figure 6 (a) describes the change in OVR ( $\varrho$ ) with respect to $\Delta C_2$  which is a variable capacitor. This result is compatible with the minor variation in  $\Delta C_2$  the change in output voltage ripples ( $\varrho$ ) also results which suggests with improved  $\Delta C_2$  the ( $\varrho$ ) is also minimized. Figure 6 (b) explains the change in OVR ( $\varrho$ ) with the variation in switching frequency. In this result, it is clear that by decreasing the switching frequency, the change in OVR ( $\varrho$ ) decreases. Clearly, increase the switching frequency the ( $\varrho$ ) is diminishing. In Figure 6 (c) shows not only change in variable capacitor but also variation in the value of switching frequency. This Figure commensurate that how much change in switching frequency causes the change in OVR ( $\varrho$ ) to occur. This Figure categorically defines that the change in OVR ( $\varrho$ ) is reduced by increasing the value of switching frequency and variable capacitor. In boost condition of SEPIC converter, Figure 6 (d) describes the change in OVR( $\varrho$ ) with respect to  $\Delta C_2$ , which is a variable capacitor. This result is compatible with the minor variation in  $\Delta C_2$  the change in output voltage ripples ( $\varrho$ ) is also changing means with the improved  $\Delta C_2$  the ( $\varrho$ ) is also minimized. increasing the switching frequency and variable capacitor.

(c) Graph of Variable Capacitor and switching frequency

(f) Graph of Variable Capacitor and Switching frequency Figure 6. change in output voltage ripple (Q) of buck and boost modes in IISM-CCM of SEPIC

converter. (a) reports the result of a variable capacitor, (b) defines the result of a variable switching frequency and(c) represents the result of variable capacitor and switching frequency in buck mode while (d) states the result of a variable capacitor, (e) narrates the result of variable switching frequency and (f) defines the result of a variable capacitor and switching frequency in boost mode.

Figure 6(e) explains the change in OVR ( $\varrho$ ) with the variation in switching frequency. In this result, it is clear that by varying the switching frequency incrementally the change in OVR ( $\varrho$ ), is decreased. With the increase in the switching frequency the change in OVR is improving. Figure 6 (f) shows not only change in variable capacitor but also changes in switching frequency. This Figure commensurate that how much change in switching frequency and capacitor will cause the change in OVR ( $\varrho$ ) to appear. This Figure depicts that the change in OVR ( $\varrho$ ) is decreasing by.

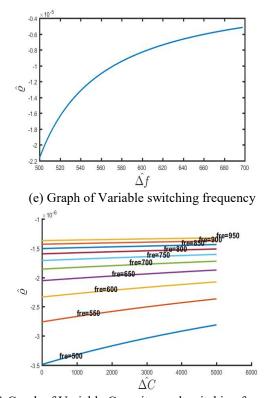

#### C. IISM-DCM

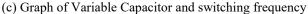

In buck condition of the SEPIC converter, Figure 7 (a) describes the change in OVR i.e.( $\varrho$ ) with respect to  $\Delta C_2$ . Figure 7 (b) explains the change in OVR ( $\varrho$ ) with the variation in switching frequency. In this result, it is clear that by decreasing the switching frequency, the change in OVR i.e. ( $\varrho$ ) decreases. In Figure 7 (c) not only the effect of change in capacitor value

#### Novel Concept of Reducing OVR at the Output of SEPIC

but also variation in the value of switching frequency is presented. This Figure commensurate that change in capacitor value and switching frequency causes the change in ( $\varrho$ ) to occur. This Figure categorically defines that the change in OVR i.e. ( $\varrho$ ) is reduced by increasing the value of switching frequency and variable capacitor. In boost condition of SEPIC converter, Figure 7 (d) describes the change in OVR ( $\varrho$ ) with respect to  $\Delta C_2$ , which is a variable capacitor. This result shows that with the variation in  $\Delta C_2$  the change in output voltage ripples i.e. ( $\varrho$ ) also changes means with the increased the( $\varrho$ ) is further minimized. Figure 7 (e) explains the change in OVR ( $\varrho$ )with the variation in switching frequency. In this result, it is clear that by varying the switching frequency incrementally the change in OVR ( $\varrho$ ), is decreased. With the increase in the switching switching frequency the change in OVR ( $\varrho$ ).

(f) Graph of Variable Capacitor and switching frequency

Figure 7. change in output voltage ripple (Q) of buck and boost modes in IISM-CCM of SEPIC converter.(a) reports the result of a variable capacitor, (b) defines the result of a variable switching frequency and(c) represents the result of variable capacitor and switching frequency in buck mode while (d) states the result of a variable capacitor, (e) narrates the result of variable switching frequency and (f) defines the result of a variable capacitor and switching frequency in boost mode.

Figure 7 (f) shows not only change in variable capacitor but also changes in switching frequency This Figure commensurate that how much change in switching frequency and capacitor will cause the change in OVR ( $\varrho$ ) to appear. This Figure depicts that the change in OVR ( $\varrho$ ) is decreasing by increasing the switching frequency and variable capacitor.

#### 5. Conclusion

The analysis of results concludes that output voltage ripple is dependent on the values of circuit elementsi. e. capacitor and inductor. Moreover, the switching frequency can also play an effective role in minimizing the OVR. The decrease in OVR in all modes are minimized except Complete Induction Supply mode in Continuous Conduction Mode (CISM-CCM). Where increase in capacitor value and switching frequency results into an increase in the OVR in boost mode.

# 6. References

- [1]. Luigi Rubino, Beniamino Guida, Felice Liccardo, Pompeo Marino, and Alberto Cavallo. Buck-boost dc/dc converter for aeronautical applications. *In Industrial Electronics (ISIE),* 2010 IEEE International Symposium on, pages 2690–2695. IEEE, 2010.

- [2]. Zoubir Roumila, Djamila Rekioua, and Toufik Rekioua. Energy management based fuzzy logic controller of hybrid system wind/photovoltaic/diesel with storage battery. *International Journal of Hydrogen Energy*, 42(30):19525–19535, 2017.

- [3]. K. Jyotheeswara Reddy and Sudhakar Natarajan. Energy sources and multi-input dc-dc converters used in hybrid electric vehicle applications-a review. *International Journal of Hydrogen Energy*, 43(36):17387–17408, 2018.

- [4]. MEHMET AL'I O" ZC, ELI'K and AHMET SERDAR YILMAZ. Improving the incremental conductance algorithm for two-stage grid connected photovoltaic systems. *Turkish Journal of Electrical Engineering & Computer Sciences*, 26(1):442–453, 2018.

- [5]. Wang Zhifu, Wang Yupu, and Rong Yinan. Design of closed-loop control system for a bidirectional full bridge dc/dc converter. Applied Energy, 194:617–625, 2017.

- [6]. Jesus Casa Hernandez et all. Protection of a multiterminal dc compact node feeding electric vehicles on electric railway systems, secondary distribution networks, and pv systems. *Turkish Journal of Electrical Engineering Computer Sciences*, 24(4):3123–3143, 2016.

- [7]. Rishabh Kumar Rai, Abhinav Dixit, Suraj Pundhir and Joseph Peter. Advanced integrated bidirectional ac/dc and dc/dc converter for plug-in hybrid electric vehicles. In 2020 *International Conference on Futuristic Technologies in Control Systems & Renewable Energy (ICFCR), pages 1–6. IEEE*, 2020.

- [8]. Zhongming Ye, Fred Greenfeld, and Zhixiang Liang. Design considerations of a high power factor sepic converter for high brightness white led lighting applications. In Power Electronics Specialists Conference, 2008. PESC 2008. IEEE, pages 2657–2663. IEEE, 2008.

- [9]. Wensong Yu, Jih-Sheng Lai, High-efficiency dc–dc converter with twin bus for dimmable led lighting. *IEEE Trans. on Power Electronics*, 26(8):2095–2100, 2011.

- [10]. Tsai-Fu Wu. Decoding and synthesizing transformer less pwm converters. *IEEE Transactions on Power Electronics*, 31(9):6293–6304,2016.

- [11]. Dragan Maksimovic and Slobodan Cuk. Switching converters with wide dc conversion range. *IEEE Transactions on Power Electronics*, 6(1):151–157, 1991.

- [12]. Ki-Bum Park, Gun-Woo Moon, and Myung-Joong Youn. Non isolated high step-up boost converter integrated with sepic converter. *IEEE Transactions on Power Electronics*, 25(9):2266–2275, 2010.

- [13]. Jingquan Chen, Dragan Maksimovi C, and Robert Erickson. Buck-boost pwm converters having two independently controlled switches. In Power Electronics Specialists Conference, 2001. PESC. 2001 IEEE 32nd Annual, volume 2, pages 736–741. IEEE, 2001.

- [14]. Ki-Bum Park, Gun-Woo Moon, and Myung-Joong Youn. Nonisolated high step-up boost converter integrated with sepic converter. *IEEE Transactions on Power Electronics*, 25(9): 2266–2275, 2010.

- [15]. Adriano Peres, D Cruz Martins, and Ivo Barbi. Zeta converter applied in power factor correction. In Power Electronics Specialists Conference, PESC'94 Record., 25th Annual IEEE, volume 2, pages 1152–1157. IEEE, 1994.

- [16]. G"okhan C, abuk and Selc, uk Kilinc, Reducing electromagnetic interferences in flyback ac-dc converters based on the frequency modulation technique. *Turkish Journal of Electrical Engineering & Computer Sciences*, 20(1):71–86, 2012.

- [17]. S Arunraj, S Murugesan, T Uma Nandhini, and K Keerthana. A novel zeta converter with pi controller for power factor correction in induction motor. *International Journal of Scientific Research in Science and Technology*, pages 230–234, 2017.

- [18]. Rudolf P Severns and Gordon Bloom. Modern DC-to-DC switch mode power converter circuits. Van Nostrand Reinhold Company,1985.

- [19]. Sina Salehi, Behrooz Vahidi, JAFAR MILIMONFARED, MAGHDAD TAHERI, and Hadi Moradi. Analysis and design of an interleaved current-fed high step-up quasi-resonant dc-dc converter for fuel cell applications. *Turkish Journal of Electrical Engineering & Computer Sciences*, 23(Sup. 1):2182–2196, 2015.

- [20]. Peng Fangzheng Fang Xupeng Gu Bin and Gao Qi Qian Zhaoming. Z-source converter [j]. *Transactions of China Electrotechnical Society*, 2:008, 2004.

- [21]. Boris Axelrod, Yefim Berkovich, and Adrian Ioinovici. Switched-capacitor (sc)/switched inductor (sl) structures for getting hybridstep-down cuk/sepic/zeta converters. In Circuits and Systems, 2006. ISCAS 2006. Proceedings. 2006 IEEE Int. Symposiumon, pages 4–pp.

- [22]. Erickson RW. DC–DC power converters. Wiley encyclopedia of electrical and electronics engineering. 2001 Aug 21.

- [23]. Boris Axelrod, Yefim Berkovich, and Adrian Ioinovici. Switched-capacitor/switchedinductor structures for getting transformer less hybrid dc-dc pwm converters. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 55(2):687–696, 2008.

- [24]. Rana N, Kumar M, Ghosh A, Banerjee S. A novel interleaved tri-state boost converter with lower ripple and improved dynamic response. *IEEE Transactions on Industrial Electronics*. 2017 Nov 17;65(7):5456-65.

- [25]. Haidong Yu. A novel control strategy of output voltage ripple reduction in buck converters. In 2011 Twenty-Sixth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pages 1910–1914. IEEE, 2011.

- [26]. Yu Krasnikov. New solutions to the old problems of buck and boost converters. In Power Electronics and Applications, 2005 European Conference on, pages 10–pp. IEEE, 2005.

- [27]. Jing Wang, William G Dunford, and Konrad Mauch. Analysis of a ripple-free input-current boost converter with discontinuous conduction characteristics. *IEEE Transactions on Power Electronics*, 12(4):684–694, 1997.

- [28]. Mustafa A Al-Saffar, Esam H Ismail, Ahmad J Sabzali, and Abbas A Fardoun. An improved topology of sepic converter with reduced output voltage ripple. *IEEE Transactions on Power Electronics*, 23(5):2377–2386, 2008.

- [29]. Gu W, Zhang D. Designing a SEPIC converter. Excellent design guidelines, national semiconductor in application note. pages 1–6. Apr 30. 2008.

- [30]. Babaei E, Mahmoodieh ME. Calculation of output voltage ripple and design considerations of SEPIC converter. *IEEE Trans. on Industrial Electronics*. 61(3):1213-22. Jul 29;2013.

- [31]. Mohanty G. SEPIC Based Multi Input Dc-Dc Converter. In2019 IEEE 5th International Conference for Convergence in Technology (I2CT) 2019 Mar 29 (pp. 1-4). IEEE.

- [32]. Budi Amri, Mochamad Ashari, et al. The comparative study of buck-boost, cuk, sepic and zeta converters for maximum power point tracking photovoltaic using p&o method. *In 2015 2nd International Conference on Information Technology, Computer, and Electrical Engineering (ICITACEE)*, pages 327–332. IEEE, 2015.

- [33]. Liu Shulin, Li Yan, and Liu Li. Analysis of output voltage ripple of buck dc-dc converter and its design. *In Power Electronics and Intelligent Transportation System (PEITS), 2009* 2nd International Conference on, volume 2, pages 112–115. IEEE, 2009.

- [34]. Qing Hua Shang, Wenjie Cao, Zhen Huang, Xiaoqing Zhang, Tao Shen, Chao Hu, Xinlao Wei, Yipu Liu, and Mengxue Zan. The studyof a digital equivalent capacitor circuit. *International Journal of Hybrid Information Technology*, 7(3):1–8, 2014.

- [35]. Programmable capacitors. www.ixysic.com/Products/ProgCap.htm, 2010 (accessed January 13, 2020).

- [36]. Ebrahim Babaei, Mir Esmaeel Seyed Mahmoodieh, and Hamed Mashinchi Mahery. Operational modes and output-voltage-ripple analysis and design considerations of buck– boost dc–dc converters. *IEEE Transactions Industrial Electronics*, 59(1):381–391, 2011.

- [37]. Ebrahim Babaei and Mir Esmaeel Seyed Mahmoodieh. Analysis and investigation of energy transmission process in different operating modes of sepic converter. *IET Power Electronics*, 7(4):819–828, 2014

**Danish IQBAL**, He received the B.Sc. degree in electrical engineering from the National Fertilizer Corporation Institute of Engineering and Technology (NFC-IET) Multan, Pakistan in 2015. He is currently working towards his M.S. Electrical Engineering degree in the National Fertilizer Corporation Institute of Engineering and Technology (NFC-IET) Multan, Pakistan. His research interests include, Power electronics, Power Inverters etc.

**Muhammad Siddique** received his B.Sc. degree in electrical engineering from the Bahauddin Zakariya University Multan, Pakistan in 2005. He received his M.Sc. degree in Power engineering from Pakistan Institute of Engineering and Applied Sciences Islamabad, Pakistan in 2007 and Ph.D. Degree from same institute in 2018. He has a teaching experience of more than 16 years. His research interests include, Artificial Neural Networks, Power electronics, Power Converters, Nonlinear Control etc.

**Muhammad Kamran Liaqat Bhatti** is currently working as Associate Professor at Department of Electrical Engineering NFC IET Multan Pakistan. He did his PhD, Masters from Nizhni Novgorod Technical University while Bachelor degrees in Electrical Engineering from Ivanovo State Power University Russia. His research interest includes thermal power systems and renewable energy.

**Muhammad Akmal Chaudhary** received the master's and Ph.D. degrees in electrical and electronic engineering from Cardiff University, Cardiff, U.K., in 2007 and 2011 respectively. From October 2011 to September 2012, he was a Postdoctoral Research Associate at the Centre for High Frequency Engineering, Cardiff University, U.K. He is currently an Associate Professor of electrical engineering with Ajman University, United Arab Emirates. His research interests chiefly lie in the broad fields of electrical and electronic Engineering. In addition to the Engineering and Physical Sciences Research

Council (EPSRC) funded opportunity for his doctoral studies in radio frequency and microwave electronics, he has won a number of highly competitive gold medals, scholarships, and awards. He is a chartered engineer (CEng), Engineering Council, U.K., and a fellow of the Higher Education Academy (HEA), U.K.

**Abdusattar Malik** is currently working as Associate Professor at Department of Electrical Engineering BZU Multan Pakistan. He did his PhD from Beijing Institute of Technology while Master and Bachelor degrees in Electrical Engineering from Pakistan. His research interest include control system and power electronics.

**Muhammad Abrar** is currently working as Associate Professor at Department of Electrical Engineering BZU Multan Pakistan. He did his PhD in 2014 from Massey University New Zealand while Master and Bachelor degrees in Electrical Engineering from Pakistan in year 2000 and 2007, respectively.

**Mujahid Hussain** received Bachelor of Science degree (BSc) in Electrical Engineering from University of Engineering and Technology (UET) Lahore, Pakistan in 2011, Master of Science (MS) in Electronics Engineering from Ghulam Ishaq Khan Institute of Engineering Sciences and Technology (GIKI), Pakistan with distinction. He has a teaching experience of 7 years and supervised many projects related to the area of modeling, simulation of solar cell properties and photovoltaics power system. His research areas include

modeling and simulation of photovoltaic system, concentrated photovoltaic system, thin-film based PV devices, organic semiconductor devices, micro hydro power plants and power converters with renewable integration.